## **ORIGINAL ARTICLE**

# Representation of a nanoscale heterostructure dual material gate JL-FET with NDR characteristics

Amirreza Bozorgi Golafzani and Seyed Ali Sedigh Ziabari\*

Department of Electrical Engineering, Rasht Branch, Islamic Azad University, Rasht, Iran

Received 31 April 2019; revised 18 August 2019; accepted 08 October 2019; available online 12 October 2019

## Abstract

In this paper, we propose a new heterostructure dual material gate junctionless field-effect transistor (H-DMG-JLFET), with negative differential resistance (NDR) characteristic. The drain and channel material are silicon and source material is germanium. The gate electrode near the source is larger. A dual gate material technique is used to achieve upward band bending in order to access n-i-p-n structure which is caused by workfunction difference between electrodes and silicon. In JL-FETs as gate voltage increases, the electric-field intensifies and the band diagram profile starts to change. It is illustrated that, by increasing the gate voltage, the potential barrier decrease and the drain current increase. In the gate voltage of 0.64 V, due to appearance of a negative peak of electric-field and carriers transport within the field, the drain current decrease. Consequently, the NDR characteristic is achieved. With increase of the gate voltage the negative peak of electric-field and the drain current is decreased.

**Keywords:** *Dual Material Gate; Heterostructure; Junctionless Field Effect Transistor (H-DMG-JLFET); Negative Differential Resistance (NDR); Workfunction.*

#### How to cite this article

Bozorgi Golafzani AR, Sedigh Ziabari SA. Representation of a nanoscale heterostructure dual material gate JL-FET with NDR characteristics. Int. J. Nano Dimens., 2020; 11 (1): 12-17.

## INTRODUCTION

Conventional field-effect transistors have junctions. These junctions can lead or prevent current flow by applying the gate bias voltage. The junctions are made of p and n type semiconductor. Other junctions could be made through connecting metal-semiconductor which is known as Schottky junction. BJTs and MOSFETs are made of p-n junctions; JFETs have only one kind of junction. The junctionless field-effect nanowire transistors (JL-FETs) have no junctions, which is a great advantage. Conventional FETs in nano diameters need high-doping concentration around  $1 \times 10^{19}$ cm<sup>-3</sup> in two-types which faces challenges. In this event, the JL-FETs have one type doping in all regions. Since doping gradient between source and drain is zero, not only no diffusion occurs to limit fast annealing but also making short channel devices would be possible. To make a JL-FET, highdoping concentration is needed to allow current flow in ON state [1]. Choosing proper material in

the gate is used to reduce gate resistance [2]. The threshold voltage of JL-FETs increases by doping concentration [3]. As this kind of transistors have no doping gradient, thermal budget in fabricating process would be reduced. These devices are like a heavily doped resistor that controls current flow through the gate voltage and are proper candidates for future nanometer devices [1-3].

First multi-gate nanowire transistors were introduced in 1996 [4]. These structures have better controllability on the channel through the gate and as a result, they have the most roll in SCEs [5]. Using dual material gate structures in JLFET to suppress OFF-state current is crucial [6]. These structures in FETs can reduce the thermal dependency of the threshold voltage due to little surface potential changing [7]. Dual material gate FETs have some advantages like higher Ion, Ion/Ioff than single material gate [8]. In recent years devices with negative differential resistance (NDR) characteristics have attracted noticeable

\* Corresponding Author Email: *sedigh@iaurasht.ac.ir*

**This work is licensed under the Creative Commons Attribution 4.0 International License.** To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/. attention [9-11]. Some of NDR functions are voltage-controlled oscillators [9, 10], Terahertz RTDs [11], logic circuits, high frequencies and memory devices [12]. For instance, intrinsic NDR characteristics in low voltage functions [9]. Further than RTDs, researchers tried a lot to achieve NDR in other devices. For example zigzag nanoribbon graphene has been introduced recently that has NDR characteristic which could be achieved by applying the controlled potential change on the gate of the device [12]. A tunneling field-effect transistor with vertical back layer graphene and Hexagonal-Bron-Nitride was brought forward that the resonant tunneling structure shows NDR characteristics [13].

Tri-terminal  $\lambda$  transistor with GaAs and a two channel GaAs by ð dopped on GaAs layer was also investigated[14]. Structures with Real-Space-Transfer (RST) [14-17] and NDR in graphene nanoribbon superlattice field-effect transistors were studied [18]. A new FET with NDR characteristics for low-power VLSI application was simulated [19]. A laboratory report for NDR and hysteresis phenomena in OLEDs based on graphene and its effects of device performance was done and concluded this two phenomena was because of graphene resistance [20].

Instabilities related to the hot carrier effects in a semiconductor have been investigated since 1940. NDR and ionization in the bulk semiconductor have led to devices such as Gunn diode and Optical Avalanche diode. Such instabilities related to hot carrier effects in low dimensional structures have attracted attention. By applying high enough electric field in a semiconductor, new kinds of instabilities could be seen that are not visible in bulk materials. Oscillatory related to high carrier effect is one of the study cases in hetero quantum- wells [21]. Obtaining these results with abovementioned theories are achievable by the new hetero quantum-well mechanism. The devices that use RST mechanism are used in high speed applications and high frequency performance [22]. One of the most common devices that can generate millimeter wavelengths is Gunn diode which NDR is achievable by it successfully. This device is used as a local oscillator and power amplifier in the ranges of 1 to 300 GHz, It is mentionable that devices with NDR could be used in micro-wave radars [23]. The important part of each electronic device is the material that appears some unique behaviors. For fabricating a high-frequency device, NDR should

be produced in the material. One of the ways to reach this, are materials and system materials that contain two conduction bands, one band with higher electron mobility and the other one with lower electron mobility. Transferring carriers from the higher mobility band to the lower mobility band leads to NDR. By measuring I-V characteristic in a device which has proper ohmic contact, it could be understood that by applying an electric-field, its current would increase. In high electric-fields which devices with different materials are expected to be in ON state, by the continuous increment in electric field, current decreases in some devices, though NDR appears in I-V curve that changes the linearity of Ohms low [24]. Voltage-controlled NDRs are achieved in high electric fields [25]. In this paper, we represent a new JL-FET with NDR characteristic. The drain and channel material are silicon and source material is germanium. The gate electrode near the source is larger. Also, The NDR characteristic of proposed device has been investigated and analyzed.

## EXPERIMENTALS

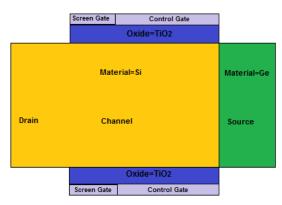

The cross section sketch of dual material JL-FET with NDR characteristic is shown in Fig. 1 It has 40 nm length and 14 nm width. The thickness of the silicon channel from silicon is 8 nm. Length of the germanium source is 5 nm and length of drain is 5 nm. By this definition we face a heterostructure JL-FET between source and channel. Germanium is one of the materials that have the potential to be used in the source side. Simulation studies show that Germanium has better ON state current in comparison with silicon [26]. It is also capable in fabricating process for transistors [27-30]. Germanium has some useful

Fig. 1. Device structure.

advantages such as high mobility of electron (3900 cm<sup>2</sup>/V s) and mobility of holes (1900 cm<sup>2</sup>/V s) in room temperature, being strained in compound of silicon in semiconductor industry as a confirmed material in CMOS [31], and it has lack of conformity with silicon (%4) [32-35]. By the above mentioned characteristics, germanium has been used as a capable material in the source side. The gate dielectric layer is Tio<sub>2</sub> which it's effective oxide thickness (EOT) is 2 nm and has length of 30 nm. Using high-k dielectric is required for scaling of oxide thickness, high performance, improved ON state current, and Gate Induced Drain Leakage (GIDL) [36,37]. All regions are n-doped with concentration  $1 \times 10^{19}$  cm<sup>-3</sup> [38].

In our proposed structure the gate electrodes are made of two different metals with non-equal length. The electrode near the source which is called control gate (CG) with the length of 20 nm and the other electrode near drain which is called screen gate (SG) with the length of 10 nm. The workfunctions of CG and SG are equal to 4.7 eV and 4.0 eV, respectively. All simulations evaluated using 2D TCAD simulator Silvaco Atlas version 5.16.2.R [39]. We comprise the effect of Fermi-Dirac statistics in the calculation of the intrinsic carrier concentration required in the expressions of Shockley-Read-Hall (SRH) recombination. For thermal motion, CONMOB and Field-Effect mobility FLDMOB were used. Because of existence high doping concentration in the Source, Channel, and Drain; BGN and Auger were chosen [40].

## RESULTS AND DISCUSSIONS

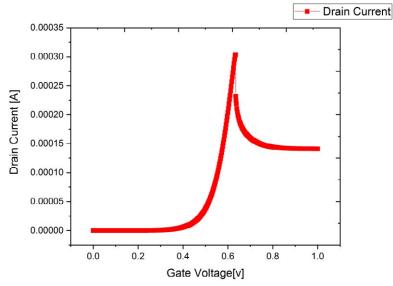

Fig. 2 shows the drain current of the proposed device. By increasing the gate voltage, the drain current increases, but in the gate voltage of 0.64 V, the I-V characteristic treatment is changed. Base on This change of behavior the voltage-controlled NDR is illustrated. For investigating the reason of NDR the energy band diagram and the electric field profile are calculated.

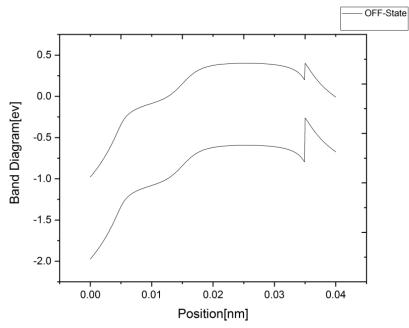

The OFF-state of device is assumed for zero gate voltage. Fig. 3 shows the OFF state energy band diagram of the proposed device. This implicates the device is n-i-p-n junction like due to energy band gap of germanium and silicon, and different workfunction of electrodes which have different length [41]. In zero bias of the gate, the device is fully depleted and there is no conduction mechanism [42].

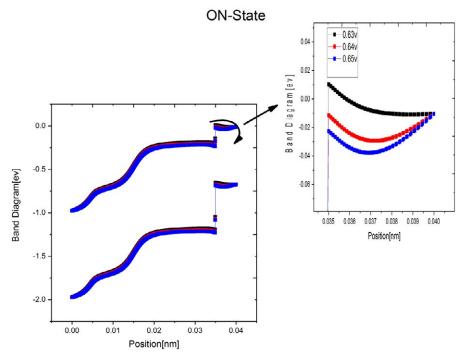

The ON-state energy band diagrams at gate voltages of 0.63, 0.64 and 0.65 V are shown in Fig. 4. This figure indicates that the band diagram profile starts to change for gate voltage more than 0.64 V.

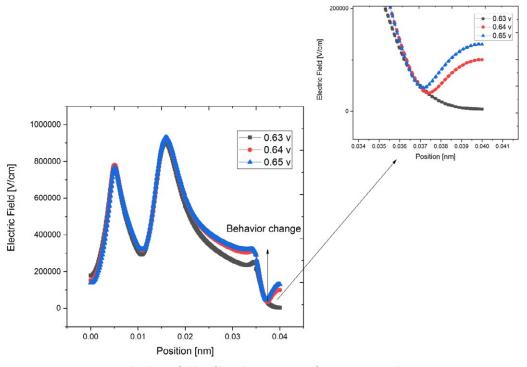

Fig. 5 illustrates the electric-Field changes of proposed device in the gate voltage of 0.63, 0.64 and 0.65 V. As know the negative peak of electricfield reduces electron velocity [43]. In high electric fields mobility of carriers would be field dependent. As electric field increases, drift velocity decreases [44, 45]. It is shown that in the gate voltage of

Fig. 2. Drain current- Gate voltage with NDR characteristic.

## AR. Bozorgi Golafzani and SA Sedigh Ziabari

Fig. 3. The OFF-state energy band diagram of the proposed device as shown in Fig. 1.

Fig. 4. The ON-state energy band diagram for the gate voltages 0.63 V, 0.64 V, and 0.65 V.

0.64 V, due to appearance of a negative peak of electric-field and carriers transport within the field, the drain current decrease. Consequently, the NDR characteristic is achieved. For increasing

of the gate voltage the negative peak of electricfield is amplified and consequently, the electron mobility and velocity and so the drain current are decreased [46].

Fig. 5. The electric field profile in the gate source of 0.63 V, 0.64 V, and 0.65 V.

#### CONCLUSION

In summary, we proposed a new heterostructure dual material gate junctionless fieldeffect transistor (H-DMG-JLFET), with negative differential resistance (NDR) characteristic. In this device the gate electrode near the source is larger than the gate electrode near the drain. Due to appearance of a negative peak of electric-field and carriers transport within the field, the drain current decrease by the gate voltage increase. Consequently, the NDR characteristic is exhibited. The proposed device would be a promising structure for achieving NDR in JL-FETs.

### DISCLOSURE STATEMENT

All authors declare that they have no conflict of interest in the publication of this manuscript.

#### REFERENCES

- [1] Colinge J. P., Lee C. W., Afzalian A., Dehdashti Akhavan N., Yan R., Ferain I., Razavi I., O'Neill B., Blake A., White M., Kelleher A-K., McCarthy B., Murphy R., (2010), Nanowire transistors without junctions. *Nat. Nano Technol.* 5: 225– 229.

- [2] Lee C. W., Ferain I., Afzalian A., Yan A., Dehdashti Akhavan N., Razavi P, Colinge J. P., (2010), Performance estimation of junctionless multigate transistors. *IEEE Transact. Elect. Dev.* 57: 620-625.

- [3] Yan R., Kranti A, Ferain I, Lee C. W, Yu R., Dehdashti Akhavan N., Razavi P., Colinge J-P, (2011), Investigation of highperformance sub-50 nm junctionless nanowire transistors. *Microelectron. Reliabil.* 51: 1166-1171.

- [4] Colinge J. P., Kranti A., Yan R., Lee C. W, Ferain I., Yu R., Dehdashti Akhavan N., Razavi P., (2011), Junctionless nanowire transistor (JNT): Properties and design guidelines. *Solid. State. Electron.* 65–66: 33-37.

- [5] Colinge J. P., Bale X., Bayot V., Grivei E., (1996), A silicon-oninsulator quantum wire. *Solid-State Elect.* 39: 49-51.

- [6] Lee C. W., Yun S. R. N., Yu C. G, Park J-T., Colinge J. P., (2007), Device design guidelines for nano-scale MuGFETs. *Solid-State Elect.* 51: 505–510.

- [7] Qian X., Yang Y., Zhu Z., Zhang S. L., Wu D., (2011), Evaluation of DC and AC performance of junctionless MOSFETs in the presence of variability. *IEEE International Conference on IC Design & Technology.*

- [8] Akarvardar K., Mercha K., Simoen E., Subramanian V., Claeys C., Gentil P., Cristoloveanu S., (2007), High-temperature performance of state-of-the-art triple-gate transistors. *Microelectron. Reliabi.* 47: 2065-2069.

- [9] Lee K., Lee J., Park J., Yang K., (2015), A novel Ku-band RTDbased quadrature VCO for low power applications. *IEEE*. *Microwave. Wireless. Co.* 25: 328-330.

- [10] Sedigh Ziabari S. A., Tavakoli Saravani M. J., (2017), A novel lightly doped drain and source Carbon nanotube field effect transistor (CNTFET) with negative differential resistance. *Int. J. Nano Dimens.* 8: 107-113.

- [11] Okada K., Kasagi K., Oshima N., Suzuki S., Asada M., (2015), Resonant-tunneling-diode terahertz oscillator using patch antenna integrated on slot resonator for power radiation. *IEEE Trans. THz Sci. Technol.* 5: 613-618.

- [12] Kumar A., Kumar V., Agarwal S., Basak A., Jain N., Bulusu A., Manhas S. K., (2014), Nitrogen-terminated semiconducting zigzag GNR FET with negative differential resistance. *IEEE Trans. Nanotechnol.* 13: 16-22.

- [13] Kang S., Fallahazad B., Kayoung L., Movva H., (2015), Bilayer graphene-hexagonal boron nitride heterostructure negative differential resistance interlayer tunnel FETs. *IEEE Elect. Device Let.* 36: 405-407.

- [14] Yu X., Mao L. H., Guo W. L., Zhang S. L., Xie S., Chen Y., (2010), Monostable–bistable transition logic element formed by tunneling real-space transfer transistors with negative differential resistance. *IEEE Elect. Dev. Let.* 31: 1224-1226.

- [15] Laskar J., Bigelow J. M., Leburton J., Kolodzey J., (1992), Experimental and theoretical investigation of the DC and high-frequency characteristics of the negative differential resistance in pseudomorphic AlGaAs/InGaAs/GaAs MODFET's. *IEEE Trans. Elect. Devices.* 39: 257-263.

- [16] Wu C. L., Hsu W. C., (1996), Enhanced resonant tunneling real-space transfer in  $\delta$ -doped GaAshGaAs gated dualchannel transistors grown by MOCVD. *IEEE Trans. Elect. Dev.* 43: 207-212.

- [17] Chen Y. W., Hsu W. C., Shieh H. M., Lin Y. S., Li Y. J., Wang T. B., (2002), High breakdown characteristic δ-doped InGaP/ InGaAs/AlGaAs tunneling real-space transfer HEMT. *IEEE Trans. Elect. Dev.* 49: 221-225.

- [18] Chang S., Zhao L., Lv Y., Wang H., Huang Q., He J., (2015), Negative differential resistance in graphene nanoribbon superlattice field-effect transistors. *Micro & Nano Lett.* 10: 400-403.

- [19] Molaei Imenabadi R., Saremi M., (2017), A Resonant tunneling nanowire field effect transistor with physical contractions: A negative differential resistance device for low power very large scale integeration application. J. Elect. Mater. 47: 1091-1098.

- [20] Zhang Q., Chen S., Zhang S, Shang W, Liu L, Wang M, Yu H., Deng L., Qi G, Wang L., Han S., Hu B., Kang Q., Liu Y., Yi M., Ma Y., Yang W., Feng J., Liu X., Sunc H., Huang W., (2017), Negative differential resistance and hysteresis in graphene-based organic light-emitting devices. J. Mater. Chem. 8: 1-8.

- [21] Balkan N., Ridley B. K., Vickers A. J., Division N. A. T. O. S. A., (1993), Negative differential resistance and instabilities in 2-D semiconductors. (Springer Science, Business Media, LLC, 1993).

- [22] Dorf R. C., (2006), The electrical engineering handbook: Sensors, nanoscience, biomedical engineering, and instruments. (CRC. Press 2006).

- [23] Sze S. M., Ng K. K., (2007), Physics of semiconductor devices, third ed. (John Wiley and Sons, Inc. publication, 2007).

- [24] Sze S. M., (1981), Physics of semiconductor devices, 2nd ed. (John Wiley- Interscience, 1981).

- [25] Ridley B. K., (1963), Specific negative resistance in solids. Proc. Phys. Soc. 82: 954-966.

- [26] Ionescu A-M., Riel H., (2011), Tunnel field-effect transistors as energy-efficient electronic switches. *Nature*. 479: 329-337.

- [27] Wang D., Wang Q., Javey A., Tu R., Daia H., (2003), Germanium nanowire field-effect transistors with SiO<sub>2</sub> and high-k HfO, gate dielectrics. *Appl. Phys. Lett.* 83: 2432-2434.

- [28] Greytak A-B., Lauhon L-J., Gudiksen M-S., Liebera C-M., (2004), Growth and transport properties of complementary germanium nanowire field-effect transistors. *Appl. Phys. Lett.* 84: 4176-4178.

- [29] Ahn Y-H., Parka J., (2007), Efficient visible light detection using individual germanium nanowire field effect transistors. *Appl. Phys. Lett.* 91: 162102-162104.

- [30] Zhang L., Tu R., Dai H., (2006), Parallel core-shell metaldielectric-semiconductor germanium nanowires for highcurrent surround-gate field-effect transistors. *Nano Lett.* 6: 2785-2789.

- [31] International Technology Roadmap for semiconductors, <u>http://www.itrs.net/</u>.

- [32] Gudiksen M., Lauhon L., Wang J., Smith D., Lieber C., (2002), Growth of nanowire superlattice structures for nanoscale photonics and electronics. *Nature*. 415: 617–620.

- [33] Bjork M. T., Ohlsson B. J., Sass T., Persson A. I., Thelander C., Magnusson M. H., Deppert K., Wallenberg L. R., Samuelson L., (2002), One dimensional steeplechase for electrons realized. *Nano Lett.* 2: 87-89.

- [34] Goldthorpe I. A., Marshall A. F., McIntyre P. C., (2008), Synthesis and strain relaxation of Ge-Core/Si-shell nanowire arrays. *Nano Lett.* 8: 4081-4086.

- [35] Chen L., Fung W. Y., Lu W., (2013), Vertical nanowire heterojunction devices based on a clean Si/Ge interface. *Nano Lett.* 13: 5521-5527.

- [36] Chau R., Brask J., Datta S., Dewey G., Doczy M., Doyle B., Kavalieros J., Jin B., Metz M., Majumdar A., Radosavljevic M., (2005), Application of high-k gate dielectrics and metal gate electrodes to enable silicon and non-silicon logic nanotechnology. *Microelect. Eng.* 80: 1-6.

- [37] Rahi S. B., Asthana P., Gupta S., (2017), Heterogate junctionless tunnel field-effect transistor: Future of lowpower devices. J. Comput. Electron. 16: 30–38.

- [38] Saib S. S., Srivastava A., (2015), A junctionless MOSFET with a triple-material gate. J. Comput. Theoret. Nanosci. 12: 2616–2621.

- [39] Silvaco, Version 5.15.32. R., (2009), <u>http://www.silvaco.</u> <u>com</u>.

- [40] Wangand C. W, Chu H., Lai Y. S., (2008), Dual workfuction metal gate dielectric. US patent no.7381619B2.

- [41] Molaei Imen Abadi R., Sedigh Ziabari S. A., (2016), Representation of type I heterostructure junctionless tunnel field effect transistor for high-performance logic application. *Appl. Phys. A*.122: 616-622.

- [42] Gundapaneni S., Ganguly S., Kottantharayil A., (2011), Bulk planar junctionless transistor BPJLT: An attractive device alternative for Scaling. *IEEE Electr. Dev. Lett.* 32: 261-263.

- [43] Molaei Imen Abadi R., Sedigh Ziabari S. A., (2016), Improved performance of nanoscale junctionless tunnel field-effect transistor based on gate engineering approach. *Appl. Phys. A.* 122: 988-997.

- [44] Molaei Imen Abadi R., Sedigh Ziabari S. A., (2017), A comparitive numerical study of junctionless and p-i-n tunneling carbon nanotube field effect transistor. J. Nano Res. 45: 55-75.

- [45] Pierret. R. F., (1996), Semiconductor device fundamental. (ADDISON-WESLEY PUBLISHING COMPANY, 2nd edition, (April 12).

- [46] Maiti C. K, Armstrong G. A., (2001), Application of silicongermanium heterostructures devices. (CRC. press, 2001).