# SHORT COMMUNICATION

# Design, simulation and analysis of high-K gate dielectric FinField effect transistor

# Marupaka Aditya<sup>1</sup>, Karumuri Srinivasa Rao<sup>1,\*</sup>, KondaviteeGirija Sravani<sup>1, 2</sup>, Koushik Guha<sup>2</sup>

<sup>1</sup>MEMS Research Center, Department of Electronics and Communication Engineering, KoneruLakshmaiah Education Foundation (Deemed to be University), Green Fields, Vaddeswaram, Andhra Pradesh, India

<sup>2</sup>National MEMS Design Center, Department of Electronics and Communication Engineering, National Institute of Technology, Silchar, Assam, India

Received 26 December 2020; revised 14 April 2021; accepted 29 April 2021; available online 08 May 2021

# Abstract

The devices with additional gates like Fin Field effect transistor (FinFET) provide higher control on subthreshold parameters and are favorable for Ultra large-scale integration. Also, these structures provide high control on current through the channel and with minimum leakage. In this paper we designed a FinFET with high-K gate dielectric material i.e Hafnium oxide as gate oxide. A comparison of similar sized transistor with Air and Silicon dioxide as gate material is performed. The comparison is mainly in terms of performance parameters like transconductance, subthreshold slope, and drain current characteristics. There is an increase in ON current on using a high-K dielectric material and subsequently an improvement in other parameters like subthreshold slope, transconductance and intrinsic gain.

Keywords: FinFET; Hafnium Oxide; High-K Dielectric; Subthreshold Slope; Transconductance.

### How to cite this article

Aditya M., Srinivasa Rao K., Sravani K.G., Guha K. Design, simulation and analysis of high-K gate dielectric FinField effect transistor. Int. J. Nano Dimens., 2021; 12(3): 305-309.

# INTRODUCTION

Fin Field effect transistors (FinFETs) have become successors of Metal oxide semiconductor Field effect transistors (MOSFETs) as they have shown alarming obstacles in nanometer scale. With the existence of two/three gates these Fin-FETs are found to drive short channel effects (SCE) like Subthreshold slope, drain induced barrier lowering (DIBL) and Subthreshold swinginabetterwaythanplanarMOSFETs.Thishelpsinenablingscalingoftransistor at nanometer technologyregimes.

Over the decades the persistent scaling of MOSFET shas resulted in intensifying of IC sand transistor density. This scaling in nanometer level is tough due to high leakage current [1-3]. The drain voltage starts to influence the channel region in scaled MOSFETs and this causes the gate to lose the channel control. Because of which thebarrier from source to drain is reduced and is termed

as Drain induced barrier lowering. This is a serious concern as we go down in technology nodes [2]. This scaling and DIBL causes increase in leakage current between source and drain. Use of high-*K* dielectric materials solves this issue by making the capacitance between channel and gate higher [3].

The thin gate oxides also solve this problem but these thin gate oxides are restricted in gate leakage. Multigate (two/three) FETs have demonstrated as substituteto traditional MOSFETs [4-6]. Extra gate(s) on channel made

transmission of drain voltage from channel.

These extra gates are made to achieve high capacitance across channel and gate. The sequalities made multi gate FETs efficient than MOSFET sw.r.t SCE. Of all Multigate FETs, FinFETs are found to be better substitute to MOSFETs because of its non-complex structure and fabrication [7-10].

In this paper, the simulation and analysis of FinFET is carried out. The  $I_p$  VS  $V_{gg'}$  subthreshold

\* Corresponding Author Email: *srinivasakarumuri@gmail.com*

**This work is licensed under the Creative Commons Attribution 4.0 International License.** To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

### M. Aditya et al.

Fig. 1. 3-Dimensional viewof proposed FinFET.

Fig. 2. Front view of proposed FinFET.

slope (SS), transconductance  $(g_m)$  characteristics of FinFET for two different materials is found. A high-K dielectric material is also used to find  $I_D$ VS  $V_{cs}$ characteristics and leakage currents.

# THE PROPOSED STRUCTURE OF FINFET

The first delineated FinFET structure is a fully depleted lean channel transistor. With the advent of short channel, the FinFETs have attracted the industry. The channel in MOSFET is horizontal whereas in case of FinFET it is vertical [11]. Therefore, the height of channel decides the width of FinFET. This is the notable property of FinFET termed as Quantization of width [12].

Beyond 1.2nm as oxide thickness is shrinked in order to have performance metrics with control on short channel effects, the silicondioxide tend to lose its dielectric properties. Hence anew dielectric material is needed to avoid electrons tunneling. Thus, a material with higher dielectric constant than  $SiO_2$  is needed. It is observed that the high-*K* dielectric materials reduce OFF current but they include the problem of trapped charges. Thus for the proper control on short channel effects without losing the dielectric properties and

Fig. 4. Top view of proposed FinFET.

to avoid problem of trapped charges  $HfO_2$  is suited as best high-K gate dielectric. The corresponding Dielectric constants of materials used are shown in Table.1. With reference to Equivalent oxide thickness, a high-K material stores increased charge [13, 14]. This is because of increase in capacitance. As the capacitance is proportional directly to materials dielectric constant, increase in dielectric constant of material increases the current. The ON current is improved when the gate material is Hafnium oxide.

In the core of channel, the quantization is practically 2-Dimensional. The FinFET device structure in 3-Dimens ions is designed in 3D Devedit and simulations are carried in ATLAS as shown in Fig.1. The structure is initially designed with Gate material as Air and corresponding  $I_DVSV_{cs}$  is found out. The gate material is replaced with high-*K* dielectric materials like Silicon dioxide and Hafnium oxide and the simulations are carriedout.

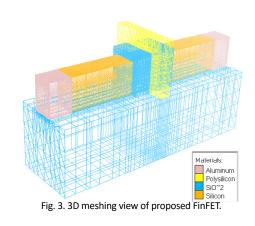

The front, meshing and top view of proposed FinFET is shown in Fig.2, 3, and 4 respectively. Table 1 shows the dielectric constants of gate mate-

Table 1. Dielectric constant of different materials.

| Dielectric<br>constant |

|------------------------|

| 1                      |

| 3.9                    |

| 22                     |

|                        |

Table 3. Physical models used in simulation.

| Model      | Description                                                                 |  |  |

|------------|-----------------------------------------------------------------------------|--|--|

| bqp        | Alternative to density<br>gradient method and<br>gives better convergence   |  |  |

| srh        | used for minority carrier<br>lifetimes                                      |  |  |

| ni.fermi   | fermi statistics effects are<br>included to find intrinsic<br>concentration |  |  |

| hcte.el    | electron temperature is specified                                           |  |  |

| bqp.ngamma | bqp γ factor for electrons<br>in enabled                                    |  |  |

| bqp.nalpha | bqp α factor for electrons<br>is enabled                                    |  |  |

| evsatmod   | defines parallel field<br>mobility model                                    |  |  |

| fldmob     | field dependent mobility<br>is invoked                                      |  |  |

rials used in this paper. The dimensions of FinFET are given in Table.2. In order to study the device performance in all dimensions, various models and methods are used. These models and methods are shown in Table. 3, and Table. 4.

# **RESULTS AND DISCUSSION**

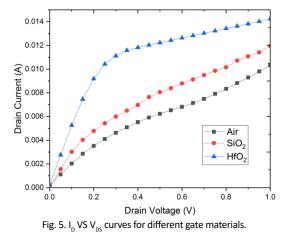

# Drain Current Characteristics

When the gate voltage is below threshold voltage, the device is said to be in OFF state and during this state minority charge carriers are the source for current flow. This generated current is also known as subthreshold current and is not required. The current generated when gate voltage is above threshold voltage is ON current.

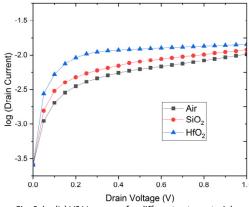

The drain current vs drain voltage for dielectric materials used is shown in Fig.5. The logarithm of drain current is also shown in Fig.6.

The drain current of FinFET for Air, Silicon dioxide and Hafnium oxide materials is shown in Table 2. Parameters used in device.

| Parameter           | Value    |

|---------------------|----------|

| Length along Z-axis | 0.1 µm   |

| Length along Y-axis | 0.02 µm  |

| Length along X-axis | 0.045 µm |

| Gate lenth          | 10 nm    |

Table 4. Methods used for simulation.

| Method   | Description                      |

|----------|----------------------------------|

| maxtrap  | specifies the repetition of trap |

|          | procedure                        |

| autonr   | Used to increase speed of        |

|          | solutions                        |

| nblockit | Used to define maximum           |

|          | number of block iterations       |

| bicgst   | Used in 3D simulations for       |

|          | bigger solutions                 |

| dvlimit  | Used for potential correction    |

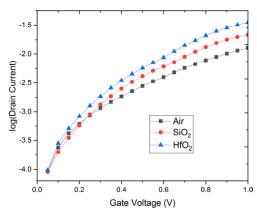

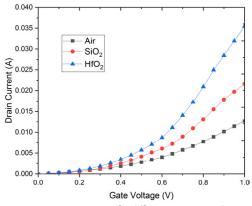

Fig.7. The dimension of gate in all the cases is kept same. From Fig.7, we can observe that the leakage current is same in both the cases [18-20], but Hafnium oxide resulted in higher ON current than silicondioxide and Air.

With the applied gate voltage, the drain current below threshold voltage also increases. This can be viewed when the  $I_D$ VS  $V_{GS}$  graphs are plotted on logarithmic scale (as shown in Fig. 8). The drain current is increasing exponentially even below threshold voltage and it is constant after  $V_{GS}$ =0.3V. The variation in these currents is analyzed by Sub threshold slope.

Fig. 6.  $log(I_D)$  VS  $V_{DS}$  curves for different gate materials.

Fig. 8.  $log(I_{D})$  VS V<sub>GS</sub> curves for different gate materials.

# Subthreshold parameters

The variation even when gate voltage is below threshold voltage the current is not zero and this is specified by a parameter called Subthreshold Slope [9] given by

Sunthreshold Slope(SS) =

$$\frac{dV_G}{d(\log_{10}(I_D))}$$

where  $V_{G}$  is applied gate voltage and  $I_{D}$  is resulting drain current.

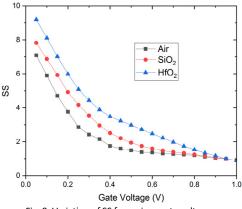

Fig.9 shows the Subthreshold curve plotted for various gate voltages. The subthreshold slope is almost constant (equal to 0 mV/dec) from 0 V to 1 V is shown. To reduce the effect of heating in devices with a short channel length, a suitable value of SS is recommended.

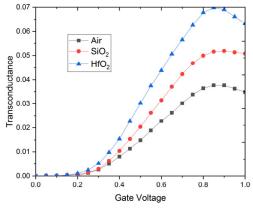

Also the Transconductance  $(g_m)$  is plotted against various gate voltages and is shown in Fig.10. For proper gain of the amplifier high transconductance is needed [15-17].

Fig. 7.  $I_D VS V_{GS}$  curves for different gate materials.

Fig. 9. Variation of SS for various gate voltages.

Fig. 10. Variation of g<sub>m</sub> for various gate voltages.

$Transconductance(g_m) = \frac{d I_D}{d(V_{DS})}$

Table.4 gives the comparison of performance

Int. J. Nano Dimens., 12 (3): 305-309, Summer 2021

#### M. Aditya et al.

| Parameter                 | Air         | SiO <sub>2</sub> | HfO <sub>2</sub> |

|---------------------------|-------------|------------------|------------------|

| I <sub>on</sub> (A)       | 0.01268     | 0.02159          | 0.03546          |

| $I_{off}(A)$              | 9.31106E-05 | 8.90169E-05      | 9.68794E-05      |

| Ion/Ioff                  | 136.182     | 242.538          | 366.022          |

| SS                        | 7.09092     | 7.82141          | 9.19874          |

| $\mathbf{g}_{\mathbf{m}}$ | 0.03757     | 0.05187          | 0.0698           |

Table 5. Comparison of performance parameters.

parameters for different dielectric materials used.

# CONCLUSION

In this paper, we have designed and simulated a new FinFET with high-*K* gate dielectric material using the concept of Effect of oxide thickness in ATLAS SILVACO and compared with similar FinFET with silicon dioxide and Air gate materials. The subthreshold slope which gives variation of drain current below threshold voltage is also calculated. The ON current is increased by a factor of ~2.79 times when the dielectric material used is HfO<sub>2</sub>. From Table.4 there is an increase of  $I_{on}/I_{off}$  SS and  $g_m$  by factors of 2.68, 1.3, and 1.857 respectively. Therefore, it can be concluded that the high-k gate dielectric material, Hafnium oxide FinFET has chosen the best material for proposed FinFET.

### CONFLICT OF INTEREST

Authors have no conflict of interest.

# REFERENCES

- Roy K., Mukhopadhyay S., Mahmoodi-Meimand H., (2003), Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. *Proc. IEEE*. 91: 305–327.

- [2] Frank D. J., Dennard R. H., Nowak E., Solomon P. M., Taur Y., Wong H. S. P., (2001), Device scaling limits of Si MOS-FETs and their application dependencies. *Proc. IEEE*. 89: 259–288.

- [3] Solomon P. M., Guarini K. W., Zhang Y., (2003), Two gates are better than one. *IEEE Circuits Devices Mag.* 19: 48–62.

- [4] Suzuki K., Tanaka T., Tosaka Y., Horie H., Arimoto Y., (1993), Scaling theory for double-gate SOI MOSFET's. *IEEE Tran. Elec. Dev.* 40: 2326–2329.

- [5] Bhattacharya D., Jha N. K., (2014), FinFETs: From devices to architectures. Adv. Electronics. 2: 1-21.

- [6] Hisamoto D., Lee W.-C., Kedzierski J., (2000), FinFET—as selfaligned double-gate MOSFET scalable to 20 nm. *IEEE Tran. Elec. Dev.* 47: 2320–2325.

- [7] Saha R., Bhowmick B., Baishya S., (2018), 3D analytical modeling of surface potential, threshold voltage, and subthreshold swing in dual-material-gate (DMG) SOI FinFETs.

J. Comp. Elect. 12: 153-162.

- [8] Saha R., Bhowmick B., Baishya S., (2017), Effects of temperature on electrical pa- rameters in GaAs SOI FinFET and application as digital inverter. *Dev. Integ. Circuit (DevIC)*. 4: 462-466.

- [9] Mendiratta N., Tripathi S., (2020), A review on performance com- parison of advanced MOSFET structures below 45 nm technology node. J. Semiconduct. 6: 1-10.

- [10] Colinge J.-P., (2008), FinFETs and other multi-gate transistors. Springer, New York, NY, USA.

- [11] Datta A., Goel A., Cakici R. T., Mahmoodi H., Lekshmanan D., Roy K., (2007), Modeling and circuit synthesis for independently controlled double gate FinFET devices. *IEEE Tran. Computer-Aided Des. Integ. Circ. Sys.* 26: 1957–1966.

- [12] Tawfik S. A., Kursun V., (2008), Low-power and compact sequential circuits with independent-gate FinFETs. *IEEE Tran. Electron Dev.* 55: 60–70.

- [13] Swahn B., Hassoun S., (2006), Gate sizing: FinFETs vs 32 nm bulk MOSFETs. Proc. 43rd IEEE Des. Automation Conf. 528–531.

- [14] Bhoj A. N., Simsir M. O., Jha N. K., (2012), Fault models for logic circuits in the multigate era. *IEEE Tran. Nanotech.* 11: 182–193.

- [15] Palanichamy V., Kulkarni N., Thankamony Sarasam A., (2019), Improved drain current characteristics of tunnel field effect transistor with heterodielectric stacked structure. *Int. J. Nano Dimens.* 10: 368-374.

- [16] Tayal S., Samrat P., Keerthi V., Vandana B., Gupta S., (2020), Channel thickness dependency of high-k gate dielectric based double-gate CMOS inverter. *Int. J. Nano Dimens.* 11: 215-221.

- [17] Khorramrouz F., Sedigh Ziabari S., Heydari A., (2018), Analysis and study of geometrical variability on the performance of junctionless tunneling field effect transistors: Advantage or deficiency? *Int. J. Nano Dimens.* 9: 260-272.

- [18] Hasan M., Kumer A., Chakma U., (2020), Theoretical investigation of doping effect of Fe for SnWO<sub>4</sub> in electronic structure and optical properties: DFT based first principle study. Adv. J. Chem. Sec. A. 3: 639-644.

- [19] Chakma U., Kumer A., Chakma K., Islam M., Howlader D., (2020), Electronics structure and optical properties of Ag-<sup>2</sup>BiO<sub>3</sub>, (Ag<sub>2</sub>) 0.88 Fe 0.12 BiO<sub>3</sub>: A first principle approach. *Adv. J. Chem. Sec. A.* 3: 542-550.

- [20] Das S., Ekka D., Roy M., (2020), Conductance and FTIR spectroscopic study of triple-ion formation of Tetrabutylphosphonium Methanesulfonate in Methylamine solution. *Chem. Methodol.* 4: 55-67.